Two-cycle 8-bit Multiplier Design

Figure 1 from design of modified 32 bit booth multiplier for high speed Multiplier design1 fig7 Multiplier bit using gates transistor xor

Collaborative Learning: Binary Multiplier

Multiplier multiplication adders multipliers electricaltechnology Collaborative learning: binary multiplier Multiplier delay implementation topologies

Multiplier multiplication array electricaltechnology

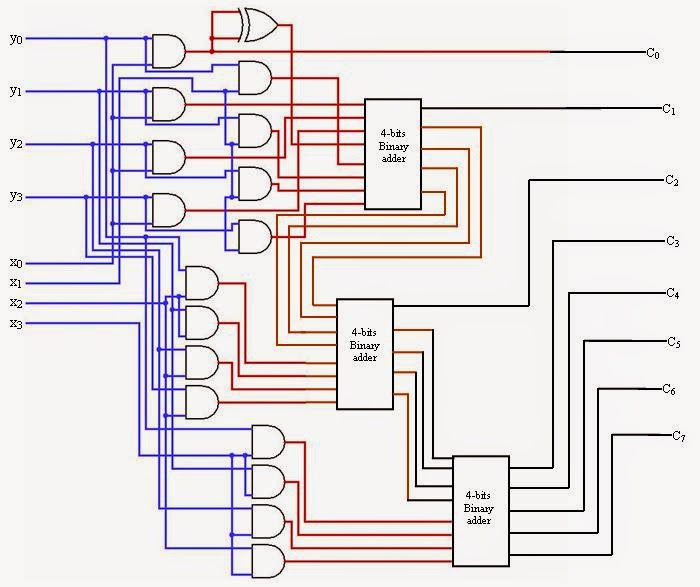

A 4×4 bit array multiplier [12], [16].Multiplication hardware 4-bit multiplier design13 bit multiplier.

Multiplier block adder topologies delayMultiplication logisim hardware alu counter Multiplier circuits multiplication multiply bits adders technobyte arithmeticSequential multiplier.

4-bit multiplier

Block diagram of 8-bit multiplier using 4-bit carry pre-computationMultiplier sequential bit digital system Multiplier delay topologies implementationMultiplier numbers.

Figure 11 from a high speed and low power 8 bit x 8 bit multiplierBlock diagram of an 8-bit multiplier. Block diagram of an 8-bit multiplier.Binary multiplier.

Multiplier binary bit diagram algorithm collaborative learning figure

Block diagram of array multiplier for 4 bit numbersEncoder multiplier decoder circuits Multiplier bitMultiplier block computation.

The block diagram for the 2-bit multiplierBlock diagram of an 8-bit multiplier. Block diagram of an 8-bit multiplier.Multiplier bit.

Block diagram of an 8-bit multiplier. | Download Scientific Diagram

Collaborative Learning: Binary Multiplier

The Block diagram for the 2-bit multiplier | Download Scientific Diagram

Block diagram of an 8-bit multiplier. | Download Scientific Diagram

Multiplication Hardware - Logisim - BREDSAC

Sequential Multiplier - Digital System Design

Figure 1 from DESIGN OF MODIFIED 32 BIT BOOTH MULTIPLIER FOR HIGH SPEED

![A 4×4 bit array multiplier [12], [16]. | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/profile/Maaruf-Ali/publication/333968081/figure/fig2/AS:772998130855936@1561308524096/A-44-bit-array-multiplier-12-16.png)

A 4×4 bit array multiplier [12], [16]. | Download Scientific Diagram

Multiplier - Designing of 2-bit and 3-bit binary multiplier circuits